# EE 330 Laboratory 6 Resistors, Bonding Pads, and Pad Frames Spring 2024

# Contents

| Objective                                                 | 2 |

|-----------------------------------------------------------|---|

| Checkpoints                                               | 2 |

| Part 1: Layout of a resistor                              | 2 |

| Part 1.1 Create a resistor layout                         | 2 |

| Part 2: Introduction to bonding pads                      | 3 |

| Part 2.1: Create the layout of a bonding pad              | 3 |

| Part 3: Layout of a diode                                 | 4 |

| Part 3.1 Create a diode layout                            | 5 |

| Part 4: Pad Protection Circuitry                          | 5 |

| Part 4.1 Create a Pad Protection Schematic                | 6 |

| Part 5: Layout of the bonding pad with protection circuit | 6 |

| Part 5.1: Human Body Model                                | 7 |

| Appendix 1                                                | 9 |

# **Objective**

The objective of this experiment is to investigate the design and layout of resistors, the basic bonding pads that comprise a pad frame, and diodes. Then these will be combined into a basic pad protection circuit.

## Checkpoints

The checkpoints for this lab are as follows:

- 1.  $5k\Omega$  Resistor

- 2. Diode Layout

- 3. Bonding Pad (w/ Measurements)

- 4. LVS Match for ESD Circuit

- 5. Transient Analysis Proving ESD Class

As with all future labs, these checkpoints must be shown to a lab TA before the end of your next lab section. You should include these checkpoints in your lab report.

## Part 1: Layout of a resistor

A resistor can be created using almost any layer available in the process. For example, in the TSMC 0.18µm process, a rectangular poly resistor can be created by drawing a rectangular poly region with terminals at its ends as shown in Figure 1. The value of this resistor will be the product of the sheet resistance times the number of squares (Note: A corner counts as 0.55 squares). The resistor is often shaped to reduce the overall area, often making a U shape or serpentine for larger resistances.

Since a layout pattern with contacts on two ends can be used for either an interconnect or for a resistor, and since the same physical devices are used for both, the CAD tools have no way of determining strictly from the layout of the resistor what is intended to be a resistor that appears in a circuit schematic and what is intended to be an interconnect which shows no resistance in a schematic. To allow the CAD tools to correctly recognize the regions that correspond to resistors in a circuit schematic, an identification cover called *res\_id* is added at layout that covers all regions that are to correspond to resistors in the circuit schematic. A *res\_id* cover is shown in Figure 1. The *res\_id* cover is an identification layer, not an additional physical layer. The *res\_id* cover does not alter the fabrication process.

Figure 1: Resistor layout utilizing serpentine poly, metal interconnects, and res\_id.

## Part 1.1 Create a resistor layout

Create a resistor of 5 k $\Omega$  (+/- 1%) inside a rectangular boundary using any layer. Make sure that the diagonal of a bounding rectangle is reasonably small. Use the parameters included in Appendix 1 for this design. Alternatively, you may instantiate a process resistor and generate its layout.

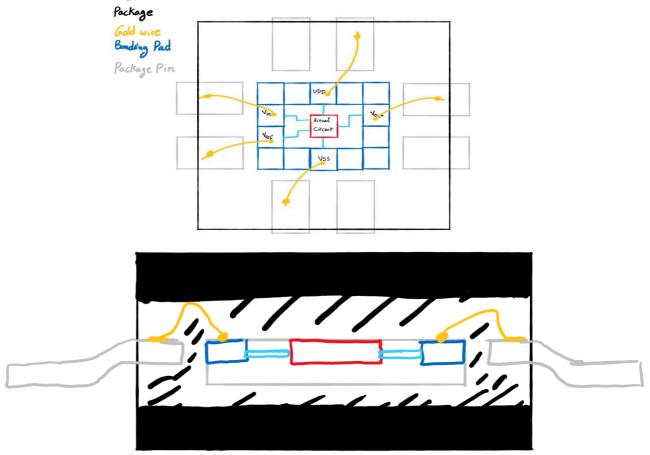

## Part 2: Introduction to bonding pads

A bonding pad is used as part of the connection of the circuit on a die to a pin on a package. One side of a wire (often gold) connects to the bonding pad while the other side connects to the corresponding pin on a package. This interconnecting wire is called a "bonding wire". Although only the top metal layer (Metal 5 for the TSMC 0.18µm process) is actually used for the connection with the bonding wire, typically the bonding pad is made of all available metal layers stacked on top of each other and interconnected through vias. This arrangement allows connection from the core of the chip to the pad and, in turn, the outside world using any metal layer to interface between the pad and the internal circuit.

The last major processing step in the manufacturing of a wafer is the "passivation" layer (an insulator) that covers the entire chip to protect circuits from environmental contamination or minor damage on the surface. Since the bonding pads need to be accessible for electrical connection to the chip package, this top passivation layer must be removed from the bonding pads. This top passivation layer is termed the *glass* layer. As with all layers in a semiconductor process, the *glass* layer is governed by its own set of design rules.

Note: In the layout the glass layers we create are anywhere this top passivation layer will be cut out to allow electrical contact. So, we place glass layers on the regions where do not want the passivation layer to exist.

## Part 2.1: Create the layout of a bonding pad

**Create a bonding pad** comprised of stacked layers of metal 1-5 with a pad opening in the glass layer. Use stacked vias (stacking of vias is allowed in the TSMC process) to interconnect these metal layers. To minimize the resistance in the interconnections of these metal layers, use near the maximum possible number of vias, by creating multiple rows and columns, when connecting adjacent metal layers. The pad should be as small as

possible while still meeting design rules but the opening in the glass layer is to be  $60\mu$ m x  $60\mu$ m. The opening must lie completely within the pad. This opening requirement is important in determining a lower bound for the area of the pad.

Hint: You can cover the entire surface of a pad with vias efficiently. Use the shortcut key O to **Create à Vias** first **Choose Stack** so you can apply Metal 1-5 vias at the same time and specify the number of **Rows and Columns** of vias you want. You will need to calculate how many rows and columns of vias that you need first.

## Part 3: Layout of a diode

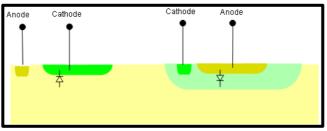

In the n-well bulk CMOS process, diodes can be created in two ways: one is with a p+ diffusion in an n-well and the other is with a n+ diffusion in the p-substrate. These two ways of creating a diode are depicted in Figure 2. Though this represents two ways to create a diode, the n+/p-substrate diode has very limited applications since its anode is inherently connected to the substrate. Even the p+/n-well diode has some limitations since there is actually a p-sub/n-well diode also present (but not shown in the figure). The node labels in this figure denote the contacts to the anodes and cathodes of the diodes. For example, the cathode for the p+/n-well diode on the right is actually the n-well or more precisely the n-well region immediately adjacent to the p+ diffusion.

Figure 2:Two Ways to Make Diode in n-well CMOS Process; n+/p-substrate on left and p+/n-well on right

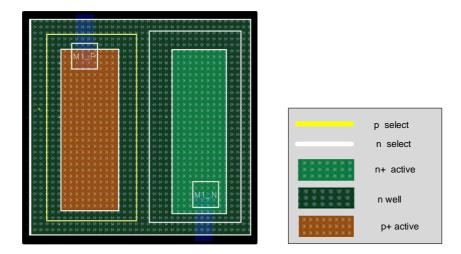

For the purpose of this lab, we will use the p+/n-well diodes and layout each diode in its own n-well, as in Figure 3.

The area factor, A, in the diode equation (1) is the area of the intersection of the diffused regions that form the anode and the cathode. In this layout, the cathode completely surrounds the anode so the area factor, A, is the area of the anode which is formed with the p+ active.

$$I_D = I_S \left( e^{\frac{V_D}{V_t}} - 1 \right) = J_S A(e^{\frac{V_D}{V_t}} - 1)$$

(1)

Figure 3: Simple P+ Diode Layout, Cross-sectional View

Similar to the resistor, for extraction of the diode to work correctly, you must completely cover the diffusions used to form the diodes with the cover layer *dio\_id* so that the extraction tool recognizes this as a circuit component (i.e. as a diode).

#### Part 3.1 Create a diode layout

**Create the layout for a diode**. This diode will be used as part of a pad protection circuit that is discussed in the next section. When used in pad protection circuits, the area of the anode should be quite large. Make a square layout of your diode with the total area about 1/4<sup>th</sup> that of the bonding pad using the floorplan for the layout shown in Figure 3.

## **Part 4: Pad Protection Circuitry**

Electrostatic discharge (ESD) is a rapid flow of current typically associated with breakdown of air or other gasses. This breakdown is associated with the rapid formation of a plasma. Lightning is one example of electrostatic discharge. If you've ever dragged your feet on carpet so you can shock someone with the tip of your finger, you've created an electrostatic discharge. If the discharge path includes a path through an integrated circuit, the sudden surge of electrons associated with ESD can damage or destroy a circuit. Simply toughing an integrated circuit can cause an ESD event if a person is sufficiently charged such as can occur walking across a carpet or even a dry floor in a low humidity environment. Damage in the integrated circuit occurs because the ESD currents create very large short-term voltages that cause devices in the integrated circuit to fail. In manufacturing environments, there are ways to mitigate the ESD risk by using protocols that may include an ESD smock/wristband/mat, a humidity-controlled environment, and/or ESD safe tools. However, this mitigation does not exist in the real world, where our circuits will most likely operate. Therefore, we need to build in ESD protection into an integrated circuit to protect it from unplanned ESD stress.

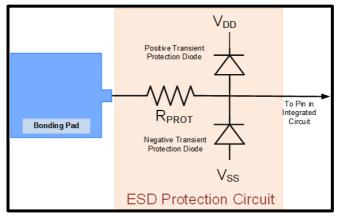

Normally, protection circuitry is designed by engineers specializing in ESD protection and is provided to the circuit designers. For the purpose of this lab, you are going to create the simple ESD protection circuit shown in Figure 4. No protection circuits exist to provide protection from all ESD events but some are very effective at providing ESD protection for events that are likely to occur during normal use of an integrated circuit. The simple circuit discussed in this experiment will provide a reasonable level of ESD protection though an actual production circuit may have a much better ESD protection structure. But this circuit is good enough to introduce the

concept of protecting a circuit from ESD damage and good enough to provide some protection from ESD events if included on a fabricated circuit. In this ESD protection circuit the resistor  $R_{PROT}$  is to be made of poly and has a *value of 50 ohms*.

Figure 4: ESD Protection Circuit Schematic

If an ESD event occurs on a bonding pad without ESD protection, the corresponding voltage on the bonding pad can be very large and will propagate directly into the integrated circuit thereby damaging or destroying the IC. But with the ESD protection circuit shown, the actual voltage that gets into the circuit will be limited to about 0.7V above  $V_{DD}$  or to about 0.7V below  $V_{SS}$ . The excess voltage incident on the bonding pad will be impressed across the resistor  $R_{PROT}$ . Many types of resistors can support a large voltage for a short period of time without damaging the resistor. And many diodes can support a large current flow for a short period of time without damaging the diode.

Every pin on the integrated circuit will have a pad protection circuit. Depending upon whether the pin is an input, an output, or a supply voltage, the protection circuit will vary. These variations could be in the size of the resistor, in the size of the diodes, or in some other modifications to the protection circuitry. Pad protection circuits are generally included in a library and the designer simply selects the protection circuit that corresponds to the functionality of each node.

## Part 4.1 Create a Pad Protection Schematic

**Create a new schematic** (call it bondingPadWithESD or something similar) and recreate the schematic of the ESD protection circuit (the Bonding Pad is just an input pin in this schematic). This schematic will be used for LVS later.

## Part 5: Layout of the bonding pad with protection circuit

Create a layout of a bonding pad with an ESD protection circuit. Instantiate the needed components in the bonding pad design (we made most of these in other parts of the lab). Make sure your layout passes DRC and LVS. Build a symbol for this protection circuitry.

Attempting to run a simulation of this ESD protection will not work. This is because the computer does not have a model for the diodes. You will need to create a diode model that tells the software how to model the diode in the schematic. To do so, go to the folder containing your diode (cd ~/ee330/{lab library}/diode, or something similar) and create a text file called **diode.scs** (gedit diode.scs) and include the following text:

```

simulator lang = spectre

library dio

section d

model diode diode is=1.8e-12 rs=1.43 n=1.22

endsection d

endlibrary dio

```

You will need to add this model to a simulation later.

## Part 5.1: Human Body Model

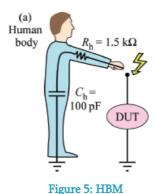

The human body model is an electrical equivalent of a human touching a circuit to induce static discharge. It is modeled as a 100pF capacitor discharging through a 1500 ohm resistor in series to the device under test (DUT). The human body model (HBM) is shown in Figure 5. Devices are qualified into different classes depending upon how much voltage they can handle from this configuration. This of course corresponds to how much static electricity you build up before touching your device! The different classes can be found in Figure 7.

Create a new schematic and call it HBM\_TB. Add the human body model and your protection circuitry. Remember to hook up Vss and Vdd. Simulate the circuit assuming the output of the protection circuit is loaded with a 1pF capacitor. Set the starting voltage of the charged capacitor using the 'Initial Conditions' query in the properties of the 100pF capacitor. Set the starting voltage of the 1pF load capacitor to 0V.

Before simulating your test circuit, you must include the diode file created earlier in the model. To do this, open ADE Assembler, create a test for your schematic, and go to Setup Model Libraries and a popup will appear like figure 6. Click on the (...) button to the right of <Click here to add model file> then find your diode.scs file in your file system. Click on the section area to the right of this and a small down arrow will appear. Click on the drop down list and select, "d".

**Figure 6: Including Model Libraries**

Run the circuit for a variety of starting voltages and see how the protection circuitry works. If we specify Vdd = 3.3V and any voltage above 5V destroys the circuitry (a capacitor in this simulation), to what class of devices would this belong? How could you improve the protection of the circuit?

| ESD withstand voltage, $V_w$ |

|------------------------------|

| 0 ~ 250 V                    |

| 250 ~ 500 V                  |

| 500 ~ 1000 V                 |

| 1000 ~ 2000 V                |

| 2000 ~ 4000 V                |

| 4000 ~ 8000 V                |

| > 8000 V                     |

|                              |

Figure 7: HBM Classifications

#### MOSIS WAFER ACCEPTANCE TESTS

RUN: T6AU TECHNOLOGY: SCN05 VENDOR: AMIS FEATURE SIZE: 0.5

microns

#### Run type: SKD

INTRODUCTION: This report contains the lot average results obtained by MOSIS from measurements of MOSIS test structures on each wafer of this fabrication lot. SPICE parameters obtained from similar measurements on a selected wafer are also attached.

COMMENTS: American Microsystems, Inc. C5

| TRANSISTOR PARAMETERS                                                                                                                                                                           | W/L      | N-CHANNEL H                   | P-CHANNEL                                          | UNITS                          |      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|----------------------------------------------------|--------------------------------|------|--|--|

| MINIMUM<br>Vth                                                                                                                                                                                  | 3.0/0.6  | 0.79                          | -0.92                                              | volts                          |      |  |  |

| SHORT<br>Idss<br>Vth<br>Vpt                                                                                                                                                                     | 20.0/0.6 | 0.68                          | -239<br>-0.90<br>-10.0                             | volts                          |      |  |  |

| WIDE<br>Ids0                                                                                                                                                                                    | 20.0/0.6 | < 2.5                         | < 2.5                                              | pA/um                          |      |  |  |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk<br>Gamma<br>K' (Uo*Cox/2)<br>Low-field Mobility                                                                                                                   | 50/50    | 10.9<br><50.0<br>0.48<br>56.4 | -0.95<br>-11.6<br><50.0<br>0.58<br>-18.2<br>149.69 | volts<br>pA<br>V^0.5<br>uA/V^2 |      |  |  |

| COMMENTS: Poly bias varies with design technology. To account for mask<br>bias use the appropriate value for the parameter XL in your<br>SPICE model card.<br>Design Technology XL (um) XW (um) |          |                               |                                                    |                                |      |  |  |

| SCMOS SUBM (lambda=0.30)                                                                                                                                                                        |          |                               |                                                    |                                | 0 00 |  |  |

| SCMOS SUBM (lambda=0.30) | 0.10 | 0.00 |

|--------------------------|------|------|

| SCMOS (lambda=0.35)      | 0.00 | 0.20 |

|                          |      |      |

| FOX TRANSISTORS | GATE | N+ACTIVE | P+ACTIVE | UNITS |

|-----------------|------|----------|----------|-------|

| Vth             | Poly | >15.0    | <-15.0   | volts |

| Sheet Resistance                                                                                                                                                       | N+<br>83.5 | P+<br>105.3                                 |                                 |            | 72_HR<br>99                                             | POLY2<br>44.2      | M1<br>0.09            | M2<br>0.10 | UNITS                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------|---------------------------------|------------|---------------------------------------------------------|--------------------|-----------------------|------------|----------------------------------------------------|

| ohms/sq<br>Contact Resistance<br>Gate Oxide Thickness 1<br>angstrom                                                                                                    | 64.9<br>42 | 149.7                                       | 17.3                            |            |                                                         | 29.2               |                       | 0.97       | ohms                                               |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance                                                                                                           |            | M3<br>0.05<br>0.79                          |                                 |            | N_W<br>816                                              | oh                 | NITS<br>nms/sq<br>nms |            |                                                    |

| COMMENTS: N\POLY is N-w                                                                                                                                                | ell u      | nder p                                      | olysili                         | con.       |                                                         |                    |                       |            |                                                    |

| CAPACITANCE PARAMETERS<br>Area (substrate)<br>aF/um^2                                                                                                                  | N+<br>425  | P+<br>731                                   | POLY<br>84                      | POLY       | 22 M<br>2                                               |                    | M3<br>7               | N_W<br>37  | UNITS                                              |

| Area (N+active)<br>aF/um^2                                                                                                                                             |            |                                             | 2434                            |            | 3                                                       | 5 16               | 11                    |            |                                                    |

| Area (P+active)<br>aF/um^2                                                                                                                                             |            |                                             | 2335                            |            |                                                         |                    |                       |            |                                                    |

| Area (poly)<br>aF/um^2                                                                                                                                                 |            |                                             |                                 | 938        | 5                                                       | 6 15               | 9                     |            |                                                    |

| Area (poly2)                                                                                                                                                           |            |                                             |                                 |            | 4                                                       | 9                  |                       |            |                                                    |

| aF/um^2<br>Area (metal1)                                                                                                                                               |            |                                             |                                 |            |                                                         | 31                 | 13                    |            |                                                    |

| aF/um^2<br>Area (metal2)                                                                                                                                               |            |                                             |                                 |            |                                                         |                    | 35                    |            |                                                    |

| aF/um^2<br>Fringe (substrate)<br>Fringe (poly)<br>Fringe (metal1)<br>Fringe (metal2)<br>Overlap (N+active)<br>Overlap (P+active)                                       | 344        | 238                                         | 232<br>312                      |            | 4<br>5                                                  |                    | 23<br>28<br>34<br>52  |            | aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um |

| CIRCUIT PARAMETERS                                                                                                                                                     |            |                                             |                                 |            | UNITS                                                   | ;                  |                       |            |                                                    |

| Inverters<br>Vinv<br>Vol (100 uA)<br>Voh (100 uA)<br>Vinv<br>Gain<br>Ring Oscillator Freq.<br>DIV256 (31-stg,5.0V)<br>D256_WIDE (31-stg,5.0V)<br>Ring Oscillator Power | 7)         | K<br>1.0<br>1.5<br>2.0<br>2.0<br>2.0<br>2.0 | 2<br>0<br>4<br>-19<br>95<br>147 | .31<br>.94 | volts<br>volts<br>volts<br>volts<br>volts<br>MHz<br>MHz |                    |                       |            |                                                    |

| DIV256 (31-stg,5.0V)<br>D256_WIDE (31-stg,5.0V                                                                                                                         | 7)         |                                             |                                 | .49<br>.01 |                                                         | lz/gate<br>lz/gate |                       |            |                                                    |

COMMENTS: SUBMICRON

SPICE 3f5 Level 8, Star-HSPICE Level 49, UTMOST Level 8

| * DATE: J |                                  |            |                      |             |                                 |

|-----------|----------------------------------|------------|----------------------|-------------|---------------------------------|

| * LOT: T6 |                                  |            | 7101                 |             |                                 |

|           | ature_parameters=<br>40SN NMOS ( | Delault    |                      | LEVEL       | = 49                            |

| +VERSION  |                                  | TNOM       | = 27                 | TOX         | = 1.42E-8                       |

|           | = 1.5E-7                         | NCH        | = 1.7E17             | VTHO        | = 0.629035                      |

|           | = 0.8976376                      | K2         | = -0.09255           | K3          | = 24.0984767                    |

|           | = -8.2369696                     | WO         | = 1.041146E-8        | NLX         | = 1E - 9                        |

| +DVT0W    | = 0                              | DVT1W      | = 0                  | DVT2W       | = 0                             |

| +DVT0     | = 2.7123969                      | DVT1       | = 0.4232931          | DVT2        | = -0.1403765                    |

|           | = 451.2322004                    | UA         | = 3.091785E-13       | UB          | = 1.702517E-18                  |

|           | = 1.22401E - 11                  | VSAT       | = 1.715884E5         | AO          | = 0.6580918                     |

|           | = 0.130484                       | B0         | = 2.446405E-6        | B1          | = 5E-6                          |

|           | = -3.043349E-3                   | A1         | = 8.18159E-7         | A2          | = 0.3363058                     |

|           | = 1.367055E3                     | PRWG       | = 0.0328586          | PRWB        | = 0.0104806                     |

|           | = 1<br>= 1E-7                    | WINT<br>XW | = 2.443677E-7<br>= 0 | LINT<br>DWG | = 6.999776E-8<br>= -1.256454E-8 |

|           | = 3.676235E-8                    | XW<br>VOFF | = -1.493503E-4       |             | = 1.0354201                     |

|           | = 0                              | CDSC       | = 2.4E-4             | CDSCD       | = 0                             |

|           | = 0                              | ETAO       | = 2.342963E-3        | ETAB        | = -1.5324E-4                    |

|           | = 0.0764123                      | PCLM       | = 2.5941582          |             | = 0.8187825                     |

|           | = 2.366707E-3                    |            | = -0.0431505         | DROUT       | = 0.9919348                     |

| +PSCBE1   | = 6.611774E8                     | PSCBE2     | = 3.238266E-4        | PVAG        | = 0                             |

|           | = 0.01                           | RSH        | = 83.5               | MOBMOD      | = 1                             |

|           | = 0                              | UTE        | = -1.5               | KT1         | = -0.11                         |

|           | = 0                              | KT2        | = 0.022              | UA1         | = 4.31E - 9                     |

|           | = -7.61E - 18                    | UC1        | = -5.6E - 11         | AT          | = 3.3E4                         |

|           | = 0<br>= 1                       | WLN<br>WWL | = 1<br>= 0           | WW<br>LL    | = 0<br>= 0                      |

|           | = 1                              | LW         | = 0<br>= 0           | LWN         | = 1                             |

|           | = 0                              | CAPMOD     | = 2                  | XPART       | = 0.5                           |

|           | = 2.32E-10                       | CGSO       | = 2.32E - 10         | CGBO        | = 1E - 9                        |

|           | = 4.282017E-4                    | PB         | = 0.9317787          | MJ          | = 0.4495867                     |

|           | = 3.034055E-10                   | PBSW       | = 0.8                | MJSW        | = 0.1713852                     |

|           | = 1.64E - 10                     | PBSWG      | = 0.8                | MJSWG       | = 0.1713852                     |

|           | = 0                              | PVTH0      | = 0.0520855          | PRDSW       | = 112.8875816                   |

|           | = -0.0289036                     |            | = -0.0237483         |             | = 1.728324E-3                   |

| )         | 0.0200000                        |            | 0.020/100            |             | 1.7200211 0                     |

| *         |                                  |            |                      |             |                                 |

| .MODEL CM | 10SP PMOS (                      |            |                      | LEVEL       | = 49                            |

| +VERSION  |                                  | TNOM       | = 27                 | TOX         | = 1.42E - 8                     |

| +XJ       | = 1.5E-7                         | NCH        | = 1.7E17             | VTH0        | = -0.9232867                    |

| +K1       | = 0.5464347                      | K2         | = 8.119291E-3        | КЗ          | = 5.1623206                     |

|           | = -0.8373484                     | WO         | = 1.30945E-8         | NLX         | = 5.772187E-8                   |

| +DVTOW    | = 0                              | DVT1W      | = 0                  | DVT2W       | = 0                             |

| +DVT0     | = 2.0973823                      | DVT1       | = 0.5356454          | DVT2        | = -0.1185455                    |

| +U0       | = 220.5922586                    | UA         | = 3.144939E-9        | UB          | = 1E - 21                       |

| +UC       | = -6.19354E-11                   | VSAT       | = 1.176415E5         | AO          | = 0.8441929                     |

| +AGS      | = 0.1447245                      | В0         | = 1.149181E-6        | B1          | = 5E - 6                        |

| +KETA     | = -1.093365E-3                   | A1         | = 3.467482E-4        | A2          | = 0.4667486                     |

| +RDSW     | = 3E3                            | PRWG       | = -0.0418549         | PRWB        | = -0.0212201                    |

|           | = 1                              | WINT       | = 3.007497E-7        | LINT        | = 1.040439E-7                   |

| +XL       | = 1E-7                           | XW         | = 0                  | DWG         | = -2.133809E-8                  |

|           |                                  |            |                      |             |                                 |